# Универсальная подсистема анализа самосинхронных схем

Ю.В. Рождественский, Н.В. Морозов, Ю.А. Степченков, А.В. Рождественскене

#### Аннотация

Рассматривается анализ асинхронных схем на независимость их поведения от задержек элементов. Такие схемы называются самосинхронными. Анализ основан на построении диаграмм переходов, покрывающих все возможные состояния схемы, и относится к методам анализа схемы в глобальных состояниях. Главное преимущество этих методов заключается в их универсальности — возможности применения для анализа всех классов самосинхронных схем. Рассматриваемая подсистема АСИАН представляет собой комплекс программ, позволивший многократно сократить временные затраты на процедуру анализа по сравнению с существующими аналогами и, по существу, реализовать максимально возможную эффективность анализа.

### **I.** Введение

Самосинхронные (СС) схемы (self-time circuits) — схемы, поведение которых не зависит от задержек их элементов — имеют ряд преимуществ по сравнению с их синхронными аналогами. Они более надежны, сохраняют работоспособность (устойчивость работы без сбоев) в предельно широких условиях эксплуатации, характеризуются потенциально более высоким быстродействием и рядом других достоинств [1].

За преимущества СС-схем приходится расплачиваться более трудоемкой методологией их проектирования и необходимостью использования средств автоматизации даже для схемы, содержащей десяток вентилей.

Система автоматизированного проектирования (САПР) интегральных схем на базе СС-подхода может основываться на стандартной САПР, но при этом должны учитываться некоторые специфические особенности этой технологии [2]. Они прослеживаются на всех этапах, от моделирования и подготовки тестов до изготовления топологии. Иногда проектирование упрощается (тесты, моделирование), в других случаях — несколько усложняется (топология). Однако все эти задачи решаются в рамках имеющихся систем проектирования.

Существуют две программные подсистемы, необходимые для организации проектирования СС-схем и не покрываемые существующими средствами САПР: подсистема проверки наличия нарушений самосинхронности в проектируемой схеме и подсистема синтеза СС-схем. Настоящая статья посвящена подсистеме анализа логических схем АСИАН 1.0 для подтверждения их самосинхронности.

# II. Теоретические принципы анализа нарушений самосинхронности

Существуют методологии проектирования асинхронных схем, которые не всегда обоснованно относят к классу самосинхронных [1]. В табл. 1 представлены основные классы схем, нередко идентифицирующиеся как self-timed.

В качестве примера в первых трех строчках приведены методологии, базирующиеся на моделях с ограниченной задержкой. Подобно синхронным схемам, они вынуждены ориентироваться на худший случай срабатывания элементов (правда, не глобально, во всей схеме, а локально, в отдельных ее частях), т.е. не являются схемами, полностью независимыми от задержек элементов. Такие схемотехнические решения будем называть квазисамосинхронными (КСС). Согласованная работа отдельных частей КСС обеспечивается за счет использования линий задержек или локальных генераторов. Проектирование таких схем полностью покрывается традиционными средствами САПР.

Ко второй группе относятся СС-методологии, различающиеся типом модельного

### Классификация методологий проектирования

| Название класса                                  | Пример                    |  |  |  |  |  |

|--------------------------------------------------|---------------------------|--|--|--|--|--|

| Квазисамосинхронные методологии                  |                           |  |  |  |  |  |

| На базе использования локальных генераторов      | СС-интерфейс S/390 [3]    |  |  |  |  |  |

| Модели с ограниченной задержкой элементов        | СС-микроконвейеры и схемы |  |  |  |  |  |

|                                                  | Haffman [4]               |  |  |  |  |  |

| Объединение СС-модулей с использованием задержек | I-net [4]                 |  |  |  |  |  |

| или генераторов                                  |                           |  |  |  |  |  |

| Самосинхронные методологии                       |                           |  |  |  |  |  |

| Универсальные на базе "глобальных моделей"       | ДП (ТРАНАЛ) [5] и         |  |  |  |  |  |

| -                                                | ДР сетей Петри [4]        |  |  |  |  |  |

| Дистрибутивные схемы (ДС)                        | STG (сети Петри) [4] и    |  |  |  |  |  |

|                                                  | ДИ (ТРАСПЕКТ) [5]         |  |  |  |  |  |

| Расширенные ДС                                   | STG/IC [4]                |  |  |  |  |  |

| Комбинационные схемы                             | CAMAH [2]                 |  |  |  |  |  |

представления. Выбор модельного представления — всегда компромисс между компактностью описания и необходимой степенью подробности, достаточной как для исследования свойств, адекватных свойствам реальных схем, так и для последующей эффективной реализации (синтеза схемы).

Подробно изучены и апробированы так называемые "глобальные модели", представляющие собой упорядоченное множество полных состояний схемы (значений всех сигналов). Примерами таких моделей являются диаграммы переходов (ДП) Маллера и диаграммы разметок (ДР) сети Петри. Эти подробные описания позволяют просто представлять параллельное поведение всех типов схем: автоматных схем управления, комбинационных и схем с памятью, арбитражных схем и перестраиваемых конвейерных структур. Именно поэтому такие модели являются универсальными. С ростом размерности схемы и, в особенности, степенью ее параллельности преимущество полноты описания оборачивается недостатком – экспоненциальной сложностью описания.

Один из способов сокращения размера описания – учет специфики исследуемой схемы и использование модельного представления, эффективного именно для данного класса схем. Очень часто в практике реального проектирования встречаются схемы, обладающие однозначностью предыстории каждого переключения - так называемые дистрибутивные схемы (ДС) [5]. Этому классу схем соответствует подкласс диаграмм изменений (ДИ) – сигнальные графы (СГ), в которых все вершины – изменения имеют тип "И" а вершины типа "ИЛИ" отсутствуют. В сетях Петри используется другой подкласс ДИ – графы сигнальных переходов (Signal Transition Graphs, STG) [4], которые имеют определенные ограничения по сравнению с СГ: они не могут специфицировать поведение любой ДС. И СГ, и STG относятся к "событийным моделям", алгоритмы анализа которых существенно проще. Если сложность алгоритма анализа ДП находится в экспоненциальной зависимости от степени параллельности всей схемы, то для ДИ – зависит от степени параллельности одного события (элемента). Для схем с высоким параллелизмом количество параллельных изменений на входе одного элемента существенно меньше параллелизма всей схемы. Этим и объясняется высокая эффективность событийных моделей по сравнению с молелями в глобальных состояниях.

Для анализа чисто комбинационных схем эффективно использование функционального подхода [2]. Схемотехнические решения БИС БМК "Микроядра" не относятся ни к классу

дистрибутивных, ни к классу комбинационных схем. Поэтому было принято решение разработать подсистему анализа СС-схем АСИАН на базе универсального подхода.

Предлагаемое программное средство базируется на гипотезе Маллера: задержка срабатывания любого логического элемента может быть сколь угодно большой, но конечной, а ветвление выходного сигнала на входы всех соединенных с ним элементов удовлетворяет требованию изохронности.

В несколько упрощенной форме это положение можно переформулировать как требование конечной величины любой задержки в элементе или цепи и обеспечения одновременности поступления сигнала на входы подсоединенных элементов с точностью до времени срабатывания простейшего вентиля в используемой технологии.

Следовательно, задержка цепи приводится к выходу элемента, и разброс задержек в ветвлениях цепи меньше времени срабатывания вентиля. В принципе в широком классе применений такая гипотеза справедлива. Для того, чтобы гипотеза Маллера была справедлива и для схем субмикронного диапазона, необходимо использовать дополнительные топологические и логические приемы [6]. Возможность контроля трасс соединений в технологии БМК позволяет обеспечить правильную работу СС-схем независимо от задержек соединительных проводов после разветвления.

По Маллеру схемой называется совокупность логических элементов  $\{Z_1, .... Z_n\}$ , где каждый вход логического элемента присоединен к одному выходу, и никакие два выхода не соединены между собой. Состояние схемы в каждый момент представляет собой набор значений сигналов в ее узлах — выходах двоичных логических элементов. Входы схемы также можно считать логическими элементами без входов — генераторами нулей или единиц.

Состояние выхода элемента определяется значениями сигналов на его входах. Поведение і-того элемента схемы можно описать булевым уравнением:

$$Z'_{i} = F_{i}(Z_{1},...Z_{i},...Z_{n}),$$

где  $Z_i$ , ...  $Z_{i-1}$ ,  $Z_{i+1}$ ,.... $Z_n$  — значения сигналов во входных узлах i-того элемента в момент времени t;  $Z_i$  — значение выхода i-того элемента в момент времени t;  $Z_i$  — значение, которое должен принять выход i в следующий момент времени t';  $F_i$  — собственная функция i-того элемента.

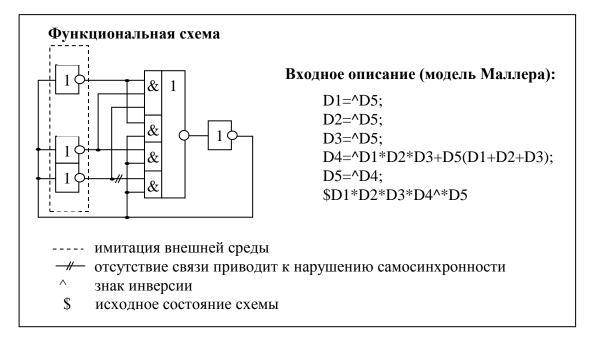

Для схемы, состоящей из n элементов, моделью Маллера называется система из n уравнений вида  $Z'_i$ , i=1,...n. В качестве примера на рис. 1 приведена схема индикатора окончания переходных процессов для трех сигналов — так называемого гистерезисного триггера (одного из наиболее распространенных элементов в СС-схемотехнике).

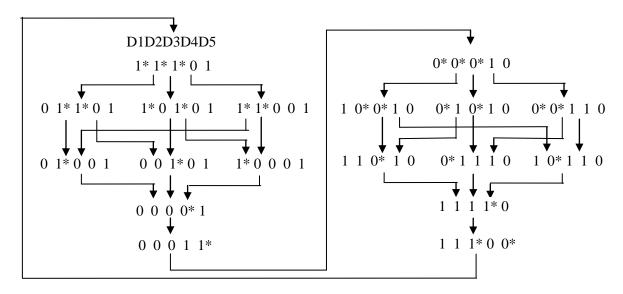

Функционирование схемы описывается процедурой ее перехода из одного состояния в другое. Наглядная форма отображения функционирования схемы, заданной моделью Маллера — ее ДП, ориентированный граф, вершины которого соответствуют состояниям схемы. Два последовательных состояния схемы на ДП соединяются дугой, а возбужденные переменные помечаются звездочками (см. рис. 2).

Критерий нарушения самосинхронности в этом случае – появление ситуации, когда одновременные переключения входов какого-либо элемента схемы вызывают противоположные по знаку переключения выхода (режим "гонок") – см. рис. 3.

Непосредственная проверка корректности системы булевых уравнений схемы (самосинхронности) осуществляется путем построения ДП, покрывающих все возможные (не зависящие от задержек) состояния, которые может принимать схема в процессе переключений согласно гипотезе Маллера, и последующей проверки условия нарушения самосинхронности для всех построенных состояний.

Полнота покрытия всех состояний достигается имитацией синхронного протокола взаимодействия с внешней средой путем "замыкания" выходного индикатора окончания переключений на входные цепи разрешения приема данных или фазы гашения.

Из сказанного видны сильные и слабые стороны такого алгоритмического подхода к проверке нарушений самосинхронности:

Рис. 1. Гистерезисный триггер на три входа

Рис. 2. Диаграмма переходов

- в качестве средства анализа используется определение понятия нарушения самосинхронности, что делает алгоритм теоретически завершенным, фундаментальным;

- в процессе работы просматриваются все временные состояния схемы без учета величины конечных задержек, что гарантирует полноту анализа;

- главный недостаток экспоненциальная зависимость числа просматриваемых состояний от числа параллельных процессов; одновременно идущих в схеме; при этом фактически включается полный перебор состояний с показателем 2N, где N – максимальная степень параллельности схемы.

Прототипом для подсистемы АСИАН была программа TRANAL в составе САПР СС-схем FORSAGE [7]. Разработанная в начале 90-х годов, эта программа была ориентирована на максимальное использование вычислительных ресурсов ПЭВМ того времени, однако реально обеспечивала решение задач, содержащих не более  $5 \div 6$  одновременных параллельных процессов СП — степень параллельности). Это обусловило сильную

```

АНАЛИЗ ЗАВЕРШЕН 08.05.2006 в 18.50.59 за

0.00.00.00

Проанализировано состояний: 26, слоев: 14

Схема полумодулярна

Параметры схемы: прошли раб.циклов - 1

В рабочем цикле: состояний - 18, слоев - 10

Ширина слоя в раб. цикле: мин. - 1, макс. - 3

а) Результат анализа: схема самосинхронна

АНАЛИЗ ЗАВЕРШЕН 08.05.2006 в 18.48.59 за 0.00.00.00

Проанализировано состояний: 9, слоев: 4

Полумодулярность нарушается в состоянии 001*11*

> конфликтное состояние:

4. D4 = 1 5. D5 = 1*

3. D3 = 1*

1. D1 = 0

2. D2 = 0

Переменная, вызвавшая конфликт: D5

Переменные, с которых снимается возбуждение:

б) Результат анализа: нарушение самосинхронности

```

Рис. 3. Результат анализа подсистемы ТРАНАЛ

ограниченность ее использования, в основном — для анализа библиотечных элементов базовых матричных кристаллов. Кроме того, работа с низкой параллельностью не позволила ее авторам обнаружить одну функциональную ошибку в цикле проверок нарушения самосинхронности. Для некоторого класса схем эта программа не обнаруживает существующих нарушений самосинхронности.

Работы по созданию реального СС-микропроцессора потребовали максимально расширить возможности программных средств для проверки самосинхронности схемных решений различных узлов и блоков микропроцессора. Первоначально была разработана подсистема анализа БТРАН, позволившая увеличить СП анализируемой схемы до 20 [8]. В рамках подсистемы АСИАН максимально возможная СП была увеличена до 24.

Вторая проблема, требовавшая решения в связи с ростом сложности схем, заключалась в трудности понимания причин нарушения самосинхронности в терминах и представлениях аппарата ДП. Требовалась мощная диагностическая система, наглядно демонстрирующая разработчику причину и предысторию процессов, приведших к нарушению самосинхронности.

Эти задачи должна была решать новая подсистема проверки нарушений самосинхронности АСИАН.

### III. Алгоритмы работы АСИАН

Анализ алгоритма ТРАНАЛ показал, что основные затраты процессорного времени и памяти уходят на формирование слоя из одновременно существующих состояний схемы. Последовательное построение этих слоев, отличающихся переключением всех (по одному) элементов из каждого состояния слоя, и формирует следующий слой, пока возможны переключения в схеме. Величина слоя состояний — экспоненциальная функция от числа параллельных процессов в слое и может достигать больших величин (иногда — десятков гигабайтов); неупорядоченный поиск состояния в слое становится бессмысленным.

Для организации упорядоченного поиска вся доступная оперативная память (ОП) ПЭВМ разбивается на 2N кластеров с помощью специально рассчитываемой хэш-функции по текущим состояниям схемы. Это позволяет сократить время доступа к конкретному состоянию до ~2N раз. Существующая версия АСИАН обеспечивает сейчас анализ схем с

разбиением ОП на кластеры до N = 24.

Красивая идея борьбы со сложностью анализа параллельных схем "степенной" формой организации памяти имеет некоторые существенные ограничения, связанные с эффективностью использования этой памяти.

Полное ее использование возможно лишь при условии, что в каждом слое состояний существует достаточное число переменных, больше N, имеющее одинаковое число состояний 0 и 1 в этом слое и к тому же, ортогональных! Это практически нереально, и приводит при больших N к не эффективному использованию оперативной памяти. Так для N=24 максимальное использование памяти практически не превышает 20%, а часть падает ниже 10%. Для того, чтобы повысить эффективность использования оперативной памяти, внутри нее выделяется специальная область со списковой организацией кластеров. Дополнительные кластеры из этой области назначаются как продолжение переполненных кластеров основной области, образуя с ними адресные списки. Такая буферизация кластеров позволяет повысить эффективность использования оперативной памяти до 80%, что существенно расширяет класс решаемых задач.

Важным аспектом использования программы АСИАН является правильный выбор величины показателя числа кластерных зон N. Практика использования программы позволяет рекомендовать следующую формулу для оптимального определения величины N:

$$N = 1.5 * P_{\text{max}}$$

где  $P_{\max}$  — максимальная параллельность исследуемой схемы, определяющаяся в модуле предварительного анализа программы АСИАН.

Полученное значение N можно рассматривать как рекомендуемое, но не всегда достаточное. Значение N не может быть более 24 (ограничение программы). При наличии небольшого объема оперативной памяти ПК использование значений N, близких к 24, может привести к неоправданному увеличению времени счета вследствие очень маленького размера кластеров. Тогда затраты на вычисление адреса кластера могут в несколько раз превысить затраты на поиск состояния в кластере. Практически рекомендуемое количество состояний в кластере (проверяется программой АСИАН перед запуском схемы на анализ) не должно быть меньше 80-100 состояний.

В ряде случаев оперативной памяти оказывается мало, и АСИАН позволяет организовать постраничное хранение массива данных слоя состояний на жестком диске, сохраняя при этом высокую эффективность доступа ко всем состояниям слоя с помощью хеш-функции страничной организации на 2К страницах. Параметр К может достигать величины 4.

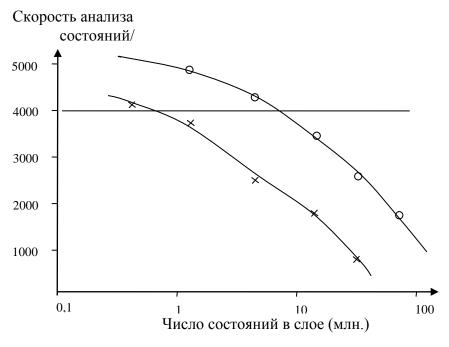

Из сказанного выше очевидно, что скорость анализа будет зависеть от размеров слоя состояний, размеров оперативной памяти, производительности ПК и настроек программы. Для практических оценок можно использовать данные, приведенные на рис. 4, отображающие зависимость скорости анализа программой АСИАН состояний слоя от размеров слоя. Результаты получены на ПК с процессором Р4 2,6 ГГц, оперативной памятью 1,5 Гб (из них при анализе использовались 1,2 Гб), размер кластера  $\sim$  100 состояний и два варианта запуска АСИАН с обычной, одностраничной, и расширенной, 16 страничной, организацией мультиплицирования оперативной памяти ПК на жестком диске.

Для исправления существующих ошибок переработан весь цикл основных проверок TRANAL с целью ускорения счета и обеспечения эффективной работы с памятью ПЭВМ.

Сравнительная оценка подсистем TRANAL, БТРАН и АСИАН приведена в таблице 2.

### IV. Диагностическая часть подсистемы АСИАН

Система диагностики TRANAL была рассчитана на анализ небольшого количества булевых уравнений и выдавала сообщение в терминах диаграмм переходов, требующих для

Рис. 4. Зависимость скорости анализа от размеров слоя

Сравнение подсистем анализа

Таблина 2

|                    |         | -                                 |                                            |                                                |                         |

|--------------------|---------|-----------------------------------|--------------------------------------------|------------------------------------------------|-------------------------|

| Система<br>анализа | СП схем | Уровень<br>тестируемых схем       | Объем памяти (тах) под один слой состояний | Количество<br>анализируемых<br>состояний в час | Операционная<br>система |

| TRANAL             | 5 ÷ 6   | Библиотечные<br>элементы (БЭ) БМК | 640 Кбит                                   | До 0,3<br>млн.                                 | DOS                     |

| БТРАН              | 12 ÷ 16 | БЭ, макроэлементы и модули        | 2 Гбайт                                    | До 1,0<br>млн.                                 | Windows 2000            |

| АСИАН              | 18 ÷ 24 | Функциональные<br>узлы и блоки    | До 48 Гбайт<br>(WinXP)                     | До 200 млн                                     | Windows<br>2000/XP      |

анализа специальной подготовки разработчика. Для больших схем эта диагностика практически теряла смысл.

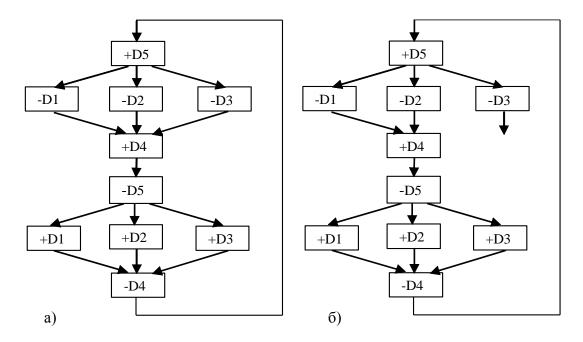

В АСИАН диагностика нарушений выполняется в виде графа переключений элементов схемы с использованием графических средств Windows. Это делает наглядным весь процесс зарождения "гонок" в динамике и позволяет определять первопричину, а не только констатировать нарушения самосинхронности, которые могут произойти значительно позднее. Такая диагностическая среда естественна для разработчиков схемы, не требует специального обучения и позволяет быстро вносить изменения в схемотехническое решение тестируемого узла.

На рис. 5 и 6 приведены диаграммы изменений для корректной (СС- схемы) Гтриггера и варианта реализации с нарушением самосинхронности (окончание переходного процесса — формирование низкого уровня на выходе элемента D3 не отслеживается). Сопоставление рис. 3,6 и рис. 5,6 делает наглядной диагностику в подсистеме АСИАН.

#### V. Выводы

- 1) Разработана подсистема анализа нарушений самосинхронности АСИАН, позволяющая практически приступить к проектированию блоков и узлов СС-схем.

- 2) Исправлены ошибки программы анализа самосинхронности TRANAL.

Рис. 5. Диаграммы изменений:

- а) самосинхронная реализация G-триггера на три входа (GI3);

- б) реализация GI3 с нарушением самосинхронности

Работа выполнена при финансовой поддержке по Государственному контракту № 1.4/03 (регистрация РАН: № 10002-251/OиТВС-04/103-098/260503-201).

### Литература

- 1. Стемиченков Ю.А., Петрухин В.С., Дьяченко Ю.Г. Опыт разработки самосинхронного ядра микроконтроллера на базовом матричном кристалле // Доклад на конференции "Проблемы разработки перспективных микроэлектронных систем-2005" Сборник научных трудов под общ. ред. А.Л. Стемпковского М.: ИППМ РАН, 2005. С. 235-242

- 2. Плеханов Л.П. САПР строго самосинхронных электронных схем РОНИС // Наст. сборн.

- 3. *Nick J.M.*, *Moore B.B.*, *et al.* S/390 Cluster Technology: Parallel Sysplex // IBM Syst. J. 1997. 36, No. 2. P.p. 172-201

- 4. *Hauck S*. Asynchronous design methodologies: An overview // Proceedings of the IEEE, 83(1), January 1995. P.p. 69-93

- 5. *Varshavsky V., Kishinevsky M., Marakhovsky V. et al.* Self-timed Control of Concurrent Processes // Kluver Academic Publishers, 1990. 245 p.

- 6. Степченков Ю.А., Денисов А.Н., Дьяченко Ю.Г., Гринфельд Ф.И. и др. Библиотека элементов базовых матричных кристаллов для критических областей применения // Сборник "Системы и средства информатики". Вып.  $14.-\mathrm{M}$ .: Наука,  $2004.-\mathrm{C}$ . 318-361

- 7. Варшавский В.И., Карпов С.А., Кондратьев А.Ю., Степченков Ю.А.. и др. Инструментальные средства автоматизации проектирования самосинхронных схем // Сборник "Системы и средства информатики". Вып. 5. М.: Наука, 1993. С. 196-213

- 8. *Морозов Н.В.*, *Рождественский Ю.В.* Средство анализа системы булевых уравнений на полумодулярность и дистрибутивность. Свидетельство об официальной регистрации программы для ЭВМ N 2001610157 от 02.2001.