(51) ΜΠΚ *H03K 3/00* (2006.01)

#### ФЕДЕРАЛЬНАЯ СЛУЖБА ПО ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ

# (12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ

(52) СПК **Н03М 3/00** (2020.02)

(21)(22) Заявка: 2019140931, 11.12.2019

(24) Дата начала отсчета срока действия патента: 11.12.2019

Дата регистрации: **31.03.2020**

Приоритет(ы):

(22) Дата подачи заявки: 11.12.2019

(45) Опубликовано: 31.03.2020 Бюл. № 10

Адрес для переписки:

119333, Москва, ул. Вавилова, 44, корп. 2, Федеральное государственное учреждение "Федеральный исследовательский центр "Информатика и управление" Российской академии наук (ФИЦ ИУ РАН)

(72) Автор(ы):

Зацаринный Александр Алексеевич (RU), Козлов Сергей Витальевич (RU), Степченков Юрий Афанасьевич (RU), Дьяченко Юрий Георгиевич (RU)

(73) Патентообладатель(и):

Федеральное государственное учреждение "Федеральный исследовательский центр "Информатика и управление" Российской академии наук" (ФИЦ ИУ РАН) (RU)

$\infty$

N

N

(56) Список документов, цитированных в отчете о поиске: RU 2469470 C1, 10.12.2012. RU 2664004 C1, 14.08.2018. RU 2427955 C2, 27.08.2011. US 20110012664 A1, 20.01.2011. CN 1977487 B, 18.08.2010.

(54) Формирователь парафазного сигнала с единичным спейсером

(57) Реферат:

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных, триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации. Технический результат сокращение сложности реализации формирователя парафазного сигнала спейсером единичным при обеспечении самосинхронности его работы с самосинхронным окружением с более высоким быстродействием.

Поставленная цель достигается тем, что в схему, содержащую инвертор, элемент И-ИЛИ-НЕ, элемент И-НЕ, информационный унарный вход, вход управления, парафазный информационный выход с единичным спейсером и индикаторный выход, введены два элемента ИЛИ-И-НЕ, вход и выход инвертора подключены к входам первой группы входов И элемента И-ИЛИ-НЕ, а индикаторный выход подключен к первым входам первых групп входов ИЛИ элементов ИЛИ-И-НЕ. 1 ил.

ပ 7

2718220

⊃ Ƴ (19) **RU** (11)

2 718 220<sup>(13)</sup> C1

(51) Int. Cl. *H03K 3/00* (2006.01)

# FEDERAL SERVICE FOR INTELLECTUAL PROPERTY

## (12) ABSTRACT OF INVENTION

(52) CPC

H03M 3/00 (2020.02)

(21)(22) Application: **2019140931**, **11.12.2019**

(24) Effective date for property rights:

11.12.2019

Registration date: 31.03.2020

Priority:

(22) Date of filing: 11.12.2019

(45) Date of publication: **31.03.2020** Bull. № **10**

Mail address:

119333, Moskva, ul. Vavilova, 44, korp. 2, Federalnoe gosudarstvennoe uchrezhdenie "Federalnyj issledovatelskij tsentr "Informatika i upravlenie" Rossijskoj akademii nauk (FITS IU RAN) (72) Inventor(s):

Zatsarinnyj Aleksandr Alekseevich (RU), Kozlov Sergej Vitalevich (RU), Stepchenkov Yurij Afanasevich (RU), Dyachenko Yurij Georgievich (RU)

(73) Proprietor(s):

Federalnoe gosudarstvennoe uchrezhdenie "Federalnyj issledovatelskij tsentr "Informatika i upravlenie" Rossijskoj akademii nauk" (FITS IU RAN) (RU)

$\infty$

N

N

(54) PARAPHRASE SIGNAL FORMER WITH SINGLE SPACER

(57) Abstract:

FIELD: pulse technique; computer engineering.

SUBSTANCE: invention relates to pulse and computer equipment and can be used in constructing self-synchronizing combinational, trigger, register and computing devices, digital information processing systems. In circuit containing inverter, AND-OR-NOT element, NAND element, information unary input, control input, paraphrase information output with single spacer and indicator output, two OR-AND-NOT elements are input, inverter input and output are

connected to inputs of the first group of inputs AND elements of AND-OR-NOT element, and indicator output is connected to first inputs of first groups of OR inputs of OR-AND-NOT elements.

EFFECT: reduced complexity of realization of a paraphrase signal generator with a single spacer while ensuring self-synchronization of its operation with a self-synchronized environment with faster operation.

1 cl, 1 dwg

\_

2718220

⊃ ~ Формирователь парафазного сигнала с единичным спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных, триггерных, регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен самосинхронный преобразователь унарного сигнала в парафазный сигнал с единичным спейсером в составе разряда параллельного регистра с однофазными входами [1, рис. 11.19], содержащий два инвертора, два элемента И-ИЛИ-НЕ и элемент И-НЕ.

Недостаток известного устройства - невозможность его использования в самосинхронном режиме работы.

5

30

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является преобразователь унарного сигнала в парафазный сигнал с единичным спейсером [2], содержащий два инвертора, два элемента И-ИЛИ-НЕ и элемент И-НЕ. При этом прототип обеспечивает возможность самосинхронной работы преобразователя унарного сигнала в парафазный с единичным спейсером, разрешающего изменение унарного входа сразу по окончании формирования рабочего состояния на парафазном выходе. Однако цена этого технического решения - увеличение в два раза аппаратных затрат (числа транзисторов, необходимых для реализации прототипа) по сравнению с его прототипом и снижение быстродействия преобразователя.

Цели прототипа, состоящие в реализации самосинхронного режима преобразователя (формирователя), разрешающего изменение унарного входа сразу по окончании формирования рабочего состояния на парафазном выходе, могут быть достигнуты с существенно меньшими аппаратными затратами.

Задача, решаемая в изобретении, заключается в сокращении сложности схемы формирователя (преобразователя) парафазного сигнала с единичным спейсером (не менее чем на 26%), разрешающего изменение унарного входа сразу по окончании формирования рабочего состояния на парафазном выходе, при обеспечении его самосинхронной работы с более высоким быстродействием (не менее чем на 25%).

Это достигается тем, что в формирователь парафазного сигнала с единичным спейсером, содержащий инвертор, элемент И-ИЛИ-НЕ и элемент И-НЕ, унарный вход, вход управления, парафазный выход с единичным спейсером и индикаторный выход, причем вход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, выход элемента И-НЕ соединен с индикаторным выходом формирователя, введены два элемента ИЛИ-И-НЕ, причем второй вход первой группы входов И элемента И-ИЛИ-НЕ подключен к выходу инвертора и второму входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, вход второй группы входов И элемента И-ИЛИ-НЕ соединен с входом управления, выход элемента И-ИЛИ-НЕ подключен к входам вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, первые входы первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ соединены с выходом элемента И-НЕ, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключен к унарному входу формирователя и входу инвертора, вход третьей группы входов ИЛИ первого элемента ИЛИ-И-НЕ соединен с выходом второго элемента ИЛИ-И-НЕ, вторым входом элемента И-НЕ и инверсной составляющей парафазного выхода, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключен к выходу первого элемента ИЛИ-И-НЕ, первому входу элемента И-НЕ и

Предлагаемое устройство обладает существенными признаками, отличающими его

прямой составляющей парафазного выхода.

от прототипа и обеспечивающими достижение заявленного технического результата. Действительно, вход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, а выход элемента И-НЕ соединен с индикаторным выходом формирователя и в прототипе. Но способ подключения выхода инвертора к входам остальных элементов схемы преобразователя сигнала в прототипе не обеспечивает его индицируемости при работе преобразователя в самосинхронном окружении. Именно подключение входа и выхода инвертора к входам первой группы входов И элемента И-ИЛИ-НЕ преобразователя позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

10

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими - парой переменных  $\{X, XB\}$ , которые в активной фазе имеют взаимоинверсные значения:  $\{X=0, XB=1\}$  или  $\{X=1, XB=0\}$ . Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если в качестве спейсерного используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, переключение в которое в самосинхронной схемотехнике должно фиксироваться индикатором окончания переходного процесса, в данном случае - окончания переключения в спейсерное состояние.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние:  $\{1,1\}$  или  $\{0,0\}$ , - называемое транзитным состоянием.

В материалах данной заявки речь идет о формировании парафазного сигнала с единичным спейсером, в дальнейшем - просто парафазного сигнала.

Унарный сигнал - обычный одиночный информационный сигнал, имеющий два возможных значения: 0 или 1. Вход управления отражает факт появления на информационном унарном входе нового значения, которое может и совпадать с предшествующим значением, своим переключением в состояние "0".

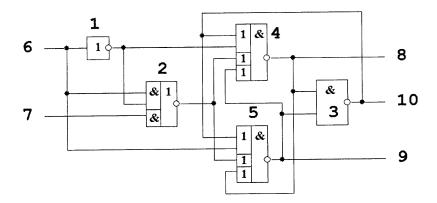

На Фиг. 1 представлена схема формирователя парафазного сигнала с единичным спейсером. Схема содержит инвертор 1, элемент И-ИЛИ-НЕ 2, элемент И-НЕ 3, два элемента ИЛИ-И-НЕ 4-5, унарный информационный вход 6, вход управления 7, парафазный информационный выход 8-9, индикаторный выход 10, вход инвертора 1 подключен к унарному входу 6, к первому входу первой группы входов И элемента И-ИЛИ-НЕ 2 и ко второму входу первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ 5, выход элемента И-НЕ 3 соединен с индикаторным выходом формирователя 10 и первыми входами первых групп входов ИЛИ первого 4 и второго 5 элементов ИЛИ-И-НЕ, второй вход первой группы входов И элемента И-ИЛИ-НЕ 2 подключен к выходу инвертора и второму входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ 4, вход второй группы входов И элемента И-ИЛИ-НЕ 2 соединен с входом управления 7, выход элемента И-ИЛИ-НЕ 2 подключен к входам вторых групп входов

ИЛИ первого 4 и второго 5 элементов ИЛИ-И-НЕ, вход третьей группы входов ИЛИ первого элемента ИЛИ-И-НЕ 4 соединен с выходом второго элемента ИЛИ-И-НЕ 5, вторым входом элемента И-НЕ 3 и инверсной составляющей парафазного выхода 9, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ 5 подключен к выходу первого элемента ИЛИ-И-НЕ 4, первому входу элемента И-НЕ 3 и прямой составляющей парафазного выхода 8.

Схема работает следующим образом. В спейсерной фазе на вход управления подается уровень логической 1, в результате обе составляющие парафазного выхода 8 и 9 принимают значение логической 1 и на индикаторном выходе 10 появляется логический 0 как признак спейсера. При этом значение сигнала на унарном входе 6 никак не влияет на значения выходов формирователя. В рабочей фазе на вход управления 7 подается значение логического 0, в результате чего парафазный выход 8, 9 переключится в состояние, соответствующее значению унарного входа 6. По окончании переключения парафазного выхода 8, 9 в рабочую фазу индикаторный выход 10 перейдет в логическую 1, отражая окончание всех переходных процессов в формирователе.

Особенности данной схемы по сравнению с прототипом следующие.

Элемент И-ИЛИ-НЕ, объединяя унарный вход, вход управления и выход инвертора, к входу которого подключен унарный вход формирователя, обеспечивает управление фазами работы формирователя и индицирование, как унарного входа, так и входа управления формирователя. Это исключает необходимость использования дополнительного Г-триггера для индикации выхода инвертора, сокращая сложность реализации самосинхронного формирователя парафазного сигнала с единичным спейсером (сложность прототипа вместе с дополнительным двухвходовым Г-триггером составляет 38 КМОП транзисторов, в то время как сложность предлагаемой схемы равна 28 КМОП транзисторам) и обеспечивая самосинхронность переключения формирователя из рабочей фазы в спейсер и обратно. Реализация предлагаемого устройства базируется на элементах, входящих в стандартные библиотеки элементов, доступные для конечных пользователей. Однако, если учитывать особенность входных сигналов, приходящих на элементы ИЛИ-И-НЕ 4 и 5, реализующих RS-триггер одновременность прихода сигналов с выходов элемента И-ИЛИ-НЕ 2 и элемента И-НЕ 3 на оба компонента RS-триггера - можно сократить число транзисторов для реализации последнего с 16 до 14, а формирователя в целом, с 28 до 26.

При этом число каскадов, перезаряжающих выходные емкости в прототипе на 25% больше чем в предлагаемом решение: 6 и 4 соответственно.

Таким образом, предлагаемое устройство обладает меньшей сложностью реализации и обеспечивает самосинхронную работу формирователя парафазного сигнала с единичным спейсером с более высоким быстродействием. Цель изобретения достигнута.

#### Источники:

35

45

- [1] Варшавский В.И., Кишиневский М.А., Мараховский В.Б. и др. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под ред. В.И. Варшавского. М.: Наука. Гл. ред. физ. мат. лит., 1986. 400 с.

- [2] Л.П. Плеханов, Ю.А. Степченков, Ю.Г. Дьяченко, А.Н. Денисов. Преобразователь унарного сигнала в парафазный с единичным спейсером. Патент РФ №2664013. Опубл. 14.08.2018 Бюл. №23. 10 с.

## (57) Формула изобретения

Формирователь парафазного сигнала с единичным спейсером, содержащий инвертор, элемент И-ИЛИ-НЕ и элемент И-НЕ, унарный информационный вход, вход управления,

#### RU 2718220 C1

парафазный информационный выход с единичным спейсером и индикаторный выход, причем вход инвертора подключен к первому входу первой группы входов И элемента И-ИЛИ-НЕ, выход элемента И-НЕ соединен с индикаторным выходом формирователя, отличающийся тем, что в схему введены два элемента ИЛИ-И-НЕ, причем второй вход первой группы входов И элемента И-ИЛИ-НЕ подключен к выходу инвертора и второму входу первой группы входов ИЛИ первого элемента ИЛИ-И-НЕ, вход второй группы входов И элемента И-ИЛИ-НЕ соединен с входом управления, выход элемента И-ИЛИ-НЕ подключен к входам вторых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ, первые входы первых групп входов ИЛИ первого и второго элементов ИЛИ-И-НЕ соединены с выходом элемента И-НЕ, второй вход первой группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключен к унарному входу формирователя и входу инвертора, вход третьей группы входов ИЛИ первого элемента ИЛИ-И-НЕ соединен с выходом второго элемента ИЛИ-И-НЕ, вторым входом элемента И-НЕ и инверсной составляющей парафазного выхода, вход третьей группы входов ИЛИ второго элемента ИЛИ-И-НЕ подключен к выходу первого элемента ИЛИ-И-НЕ, первому входу элемента И-НЕ и прямой составляющей парафазного выхода.

20

25

30

35

40

45

Фиг. 1