Самосинхронная схемотехника

Данный сайт посвящен цифровой электронной самосинхронной схемотехнике (далее просто, самосинхронной схемотехнике), служит задачам ее популяризации и содержит подборку отечественных и зарубежных публикаций по этой тематике, перевод которых выполнен инициаторами данного сайта.

Сначала необходимо определиться, что же такое схемотехника вообще и самосинхронная, в частности.

Традиционно предметом цифровой схемотехники как научно технической дисциплины считается исследование и разработка элементов и узлов (устройств) цифровых систем, а вот организацию взаимодействия устройств в составе системы к этому предмету, как правило, не относят (см., например, предисловие к книге “Райхлин В.А. Основы цифровой схемотехники. Учебное пособие для вузов. Казань: Изд-во Казан. Гос. техн. Ун-та. 2000. 352 с.»). Применительно к самосинхронной схемотехнике это утверждение неверно: организация взаимодействия узлов (устройств) в системе на базе принципа самосинхронизации является ключевым моментом этой схемотехники.

Несмотря на большое разнообразие цифровых электронных схем, все они могут быть отнесены к одному из двух классов: синхронные и асинхронные. Именно эти две альтернативные методологии решения проблемы синхронизации элементов в аппаратуре активно исследовались, начиная с середины 1950-х годов.

Синхронный подход базируется на введении в аппаратуру внешних часов – генератора тактовых импульсов. Все события в синхронной схеме могут происходить (инициироваться) только на импульсах сигнала времени внешних часов. Действительная длительность инициированных событий никак не отслеживается. Чтобы синхронизируемая аппаратура работала корректно, период синхроимпульсов выбирается из расчета на худший случай – максимально возможные времена переключения отдельных элементов и неблагоприятные сочетания условий функционирования (напряжения питания, температуры, параметров и характера распределения нагрузки, длины соединений и т.п.). Таким образом, цена корректной работы синхронной аппаратуры – недоиспользование возможностей аппаратной базы по быстродействию и обеспечение работоспособности аппаратуры в относительно узком диапазоне внешних условий эксплуатации работы (например, в диапазоне от – 5% до +5% от номинала питающего напряжения).

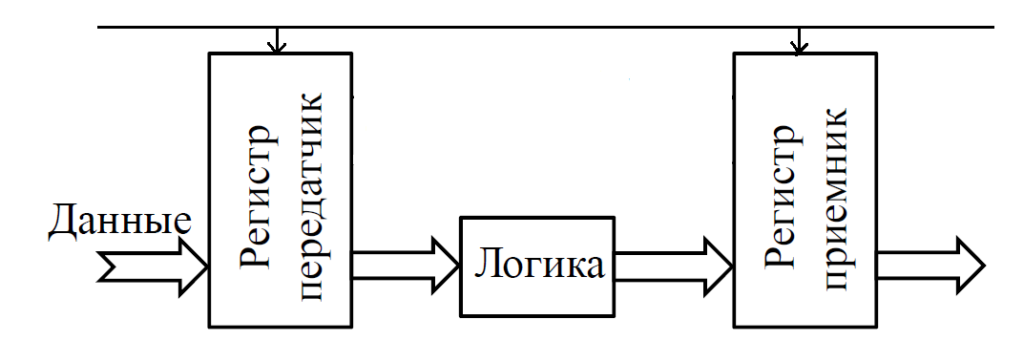

Синхронное взаимодействие устройств

CLK — синхросигнал от тактового генератора

Недостатки внешней синхронизации1

• сложность проектирования системы доставки синхросигналов в точки синхронизации из-за разброса задержек в проводах и усилителях;

• дополнительный расход мощности (до 30-40%);

• недоиспользование скоростных возможностей элементов (расчет на худший случай);

• возможность появления параметрических отказов из-за изменения условий функционирования;

• источник возникновения помех из-за одновременного срабатывания большого числа элементов;

• трудность организации согласованной работы многопроцессорной системы с индивидуальными подсистемами синхронизации из-за явления арбитража, так как не существует абсолютно надежных синхронизаторов, которые всегда обладают некоторой вероятностью сбоя. Любые такие системы подвержены сбоям.

Основное достоинство – простота проектирования устройств и минимальные затраты оборудования, что, в конечном итоге, и предопределило выбор данного вида синхронизации в качестве основного в середине 1950-ых годов.

Попытки избежать этих недостатков с помощью проектирования устройств на основе классической теории асинхронных автоматов не привели к желаемым результатам.

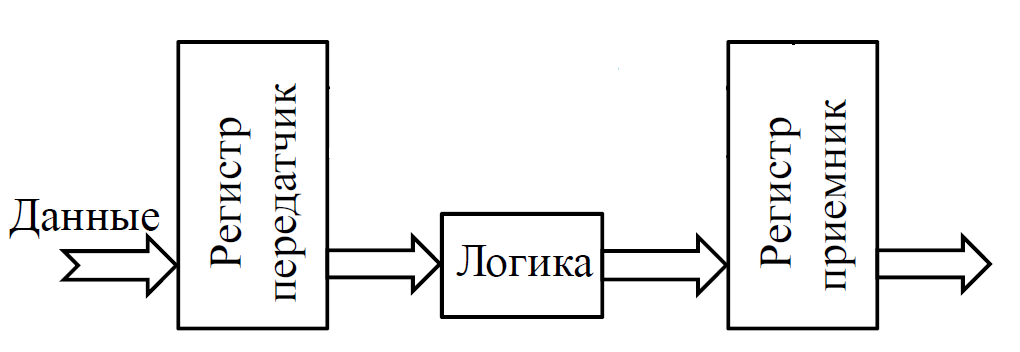

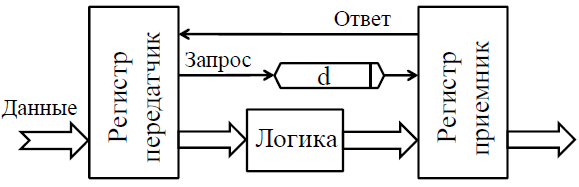

Классическое асинхронное взаимодействие устройств

(без использования сигналов “запрос-ответ”)

Переходы автомата в этой теории инициируются не сигналами от внешних часов, а сменой набора входных сигналов. Использование такого асинхронного подхода не дает увеличения быстродействия, поскольку отсутствие часов трансформируется в требование соблюдения временных интервалов между подачей соседних входных воздействий. Достоинством таких устройств является отсутствие системы доставки синхросигналов в точки синхронизации, однако сохраняются остальные недостатки синхронных устройств и дополнительно возникают новые (более сложные) проблемы: борьба с логическими и функциональными состязаниями.

Дальнейшее развитие асинхронной методологии состояло в реализации асинхронного взаимодействия устройств по принципу ‘запрос-ответ’ вместо внешних часов.

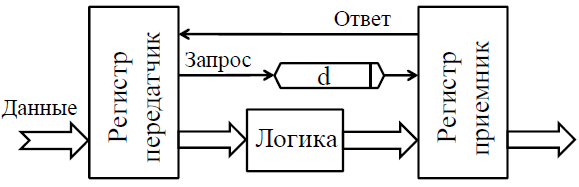

Асинхронное взаимодействие устройств

(с использованием сигналов “запрос-ответ”)

Запрос-ответное взаимодействие может быть реализовано с помощью встроенной задержки или детектора окончания переходных процессов.

Асинхронное взаимодействие устройств

(использование встроенной задержки)

•Величина встроенной задержки должна превышать максимальную задержку логической схемы и задержку записи данных в приемный регистр – приемное устройство

• Величина задержки выбирается индивидуально исходя из особенностей конкретного приемного устройства. Это позволяет повысить общий трафик системы с существенно различными скоростными характеристиками ее составляющих устройств

• В остальном, очень похоже на синхронную реализацию: длительность инициированных событий никак не отслеживается, а величина встроенной задержки выбирается из расчета на худший случай.

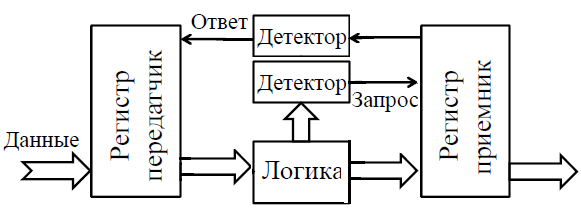

Самосинхронное взаимодействие устройств

(использование детектора окончания переходных процессов)

• детектор-запрос определяет действительное окончание переходных процессов в логической схеме – вырабатывается сигнал «запрос»

• детектор-ответ определяет действительное окончание переходных процессов в регистре приемника –

вырабатывается сигнал «ответ»

• используется избыточное кодирование данных самосинхронными кодами

• в случае отказа переходный процесс не завершается и происходит останов самосинхронной схемы (удовлетворение требованиям отказобезопасности)

Потенциальные преимущества самосинхронных (СС) схем:

• отсутствие накладных аппаратурных и энергетических расходов, связанных с реализацией «клокового дерева» – разветвленной системы синхронизации;

• максимально возможное в текущих условиях эксплуатации быстродействие;

• естественная устойчивость к параметрическим отказам, вызываемым изменением параметров элементов из-за процессов старения и неблагоприятных воздействий окружающей среды;

• максимально возможная область эксплуатации (диапазон работоспособности), определяемая только физическим сохранением переключательных свойств активных элементов базиса реализации и, как следствие, возможность работать на пониженном питающем напряжении;

• естественная самопроверяемость и самодиагностируемость по отношению к множественным константным неисправностям;

• безопасность функционирования на основе бестестовой локализации неисправностей, т.е. прекращение работы в момент отказа элемента, исключающее выдачу недостоверной информации, с одновременной локализацией места события;

• увеличение числа годных чипов за счет нечуствительности схемы к разбросу параметров;

• равномерность токопотребления;

• упрощенное тестирование: функциональные тесты одновременно являются и проверочными на неисправности;

• увеличенный срок службы за счёт нечувствительности к старению;

• простота стыковки схем между собой из-за отсутствия принудительной синхронизации, отсутствие аномального арбитража;

• высокая эффективность создания надёжных изделий:

— простота контроля и резервирования,

— нет проблемы контроля схем контроля,

— существенно меньший объем аппаратных затрат (не менее, чем в 1,5 раза) при одном и том же коэффициенте покрытия неисправностей.

Причины медленного развития самосинхронной схемотехники:

1) Традиционная направленность производственной индустрии и образования на синхронные схемы.

2) Непривычность построения и работы самосинхронных схем.

3) Отсутствие опыта построения СС-схем и отработанных СС-решений на уровне библиотечных элементов.

4) Отсутствие литературы уровня разработчика.

5) Развитие СС-схемотехники в области спецсистем, находящихся вне поля зрения разработчиков универсальных систем.

6) Большой расход оборудования или площади кристалла по сравнению с синхронными системами для тех применений, где не требуется повышенная надежность работы аппаратуры.

7) Большая сложность проектирования СС-схем и сложность разработки CАD систем (САПР – систем автоматизации проектирования).

Если п.п. 1-5 носят временный характер и отражают начальный этап становления и развития СС-схемотехники, то п. 7 является своеобразной платой за указанные эффекты. Поэтому крайне необходимо развивать методологию проектирования самосинхронных систем.

Классификация самосинхронных схем

В литературе использование термина “самосинхронный” (self-timed) носит многоплановый характер и означает лишь использование в конкретных цифровых изделиях тех или иных дополнительных средств по синхронизации работы аппаратуры по сравнению с традиционными приемами. Если подходить формально, то элементы использования СС-подхода присутствуют во всех коммерческих изделиях энергонезависимой памяти, допускающих многократную запись информации пользователем – РПЗУ (репрограммируемые постоянные запоминающие устройства; NRWM – nonvolatile read-write memory) – специфицирован режим самосинхронной записи (“self-timed write-cycle” см. MYSON TECHNOLOGY. MTV24C08/24LC08 (Revision. 1.0 11.03.1999). ) или режим самосинхронного программирования (“self-timed programming cycle ” см. Programmable Silicon Solutions. PS16256: 256K SPI Serial E2PROM with Sector Block Protection). В дополнение к управлению от системного (внекристального) генератора, в этих синхронных изделиях используется собственный внутрикристальный генератор. Действительно, такое техническое решение позволяет упростить ряд проблем, связанных с использованием глобальной синхронизации, но не исключает их полностью. В этом случае термин “self-timed logic” правильнее трактовать как “логические схемы с внутренней синхронизацией”.

В работе Self-timed interface of the input/output subsystem of the IBM eServer z900 (J.M. Hoke, P.W. Bond, R.R. Livolsi, T.C. Lo, F.S. Pidala, and G. Steinbrueck. Self-timed interface of the input/output subsystem of the IBM eServer z900// Volume 46, Number 4/5, Page 447 (2002) ) также объявлено о разработке CC-интерфейса по причине использования в устройствах ввода-вывода локального генератора.

В работе Комптона и Албискт( J. Compton, A. Albicki. Self-timed Pipeline with Adder. Proceedings GLSV’92, Second Great Lokes Symposium on VLSI Design Automation of VLSI Systems in the 90’s, February 28-29, 1992, Kalamazoo, MI, pp. 109-113) асинхронная реализация конвейера с использованием встроенных задержек объявляется как самосинхронная. Таких примеров можно привести множество. Поэтому уточним смысл термина “самосинхронная схема” и приведем классификацию асинхронных схем, в основе которой лежит гипотеза о задержках в элементах и проводах схемы.

Можно выделить четыре основные группы асинхронных схем (дополненный вариант классификации из вышеупомянутой работы Мараховского):

● схемы, не зависящие от скорости (speed—independent, SI): задержки элементов произвольные, но конечные; разброс задержек в проводах после разветвления не превышает минимальную задержку элемента;

● схемы, квазинечувствительные к задержкам (quasi—delay—insensitive, QDI): схемы, не зависящие от задержек элементов, от задержек выделенных (длинных) проводов и от задержек в проводах после разветвления, если они не критичны; могут быть спроектированы в рамках схем, не зависящих от скорости;

● схемы, нечувствительные к задержкам (delay—insensitive, DI): произвольные, но конечные задержки элементов и проводов; такие схемы дают большую избыточность;

● схемы с ограниченными задержками (boundeddelays, BD): разумное ограничение задержек элементов и проводов.

Схемы, не зависящие от скорости и квазинечувствительные к задержкам

Исторически SI-схемы первыми были предложены и теоретически обоснованы Дэвидом Маллером ‑ американским математиком и специалистом в области информатики (см. биографию на сайте). Поэтому этот класс схем иногда называют схемами Маллера (Muller’s circuits). Более конкретно используемая гипотеза о задержках звучит следующим образом:

1) величины задержек элементов могут быть произвольными, но конечными;

2) задержки элементов могут быть как инерциальными, так и чистыми;

3) задержка в проводе до разветвления приводится к задержке элемента, работающего на провод, задержка проводов после разветвления приводится к входам нагрузочных элементов, и их разность не должна превосходить минимальной задержки элемента;

4) применение встроенных задержек недопустимо.

В соответствии с гипотезой Маллера вся задержка логического элемента сосредоточена на его выходе. В то время задержки логических элементов существенно превышали задержки линий связи в рамках ИС. Схема, таким образом, могла быть охарактеризована как «совокупность логических элементов, соединенных проводами». С уменьшением топологических норм ситуация меняется: задержки логических элементов (ЛЭ) уменьшаются, и при определенных топологических нормах превалирующей может стать задержка в соединяющих линиях. Схема, таким образом, может быть охарактеризована как “совокупность проводников (линий связи), соединенных логическими элементами”. В том случае, если имеет место ветвление – выход логического элемента (ЛЭ) подключен к входам более чем одного приемного ЛЭ, – гипотеза Малера может не работать.

Для того чтобы гипотеза Маллера оставалась справедливой для схем субмикронного диапазона, либо необходимо, чтобы индикаторная часть СС-схемы учитывала задержку, вносимую линией связи, либо нужно разрабатывать новые подходы: разбивать всю ИС на отдельные зоны, в рамках которых гипотеза Маллера остается справедливой (эквихронная зона), и организовывать взаимодействие между зонами с использованием DI-подходов.

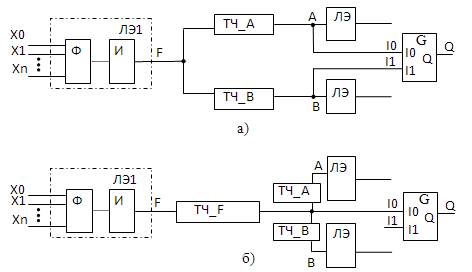

Иллюстрация сказанного приведена на рисунке ниже. Любой ЛЭ в СС-схемотехнике может быть представлен однокаскадной функциональной частью (ФЧ), инерционной частью (ИЧ) и транспортной частью (ИЧ) или транспортной задержкой. Инерционная часть отражает переходные процессы при перезаряде выходной емкости ЛЭ1, а ТЧ характеризует длинную линию – время распространения сигнала по линии связи, например, из точки F в точку A. Как правило, при формировании библиотечного элемента (БЭ) на БМК длины связей между его компонентами небольшие, он реализован на соседних ячейках, а значит, и величины ТЧ невелики. В рамках БЭ можно считать, что величина ИЧ гораздо больше ТЧ, гипотеза Маллера остается справедливой, и для фиксации окончания переходного процесса в ЛЭ1 достаточно анализировать точку F.

Варианты учета транспортной части ЛЭ при разветвлении:

а) двухпроводная индикация; б) однопроводная индикация

Это условие может нарушаться при организации связи между произвольными БЭ, которые располагаются на значительном геометрическом расстоянии друг от друга. Если точек разветвления нет (выход ЛЭ1 идет на вход только элемента ЛЭ2), величина ТЧ_A может быть сколь угодно большой. Самосинхронность при этом не нарушится, а число индицируемых точек не увеличится (индикатор анализирует точку A). В противном случае для индицируемости элемента ЛЭ1 может быть использован один из четырех способов:

а) организация двухпроводной индикации, если контроль длин соединений F-A и F-B затруднен или невозможен;

б) максимально возможное перенесение точки разветвления ближе к приемникам сигналов, при котором ТЧ_A — ТЧ_B ≤ ИЧ (ЛЭ), или другие варианты однопроводной индикации;

в) выравнивание задержек ТЧ_A = ТЧ_B (произвольное значение); при этом в качестве точки индикации может быть выбрана точка A или B;

г) если одна из линий связи характеризуется существенно большей задержкой, например, ТЧ_A >> ТЧ_B, то в качестве точки индикации выбирается точка A.

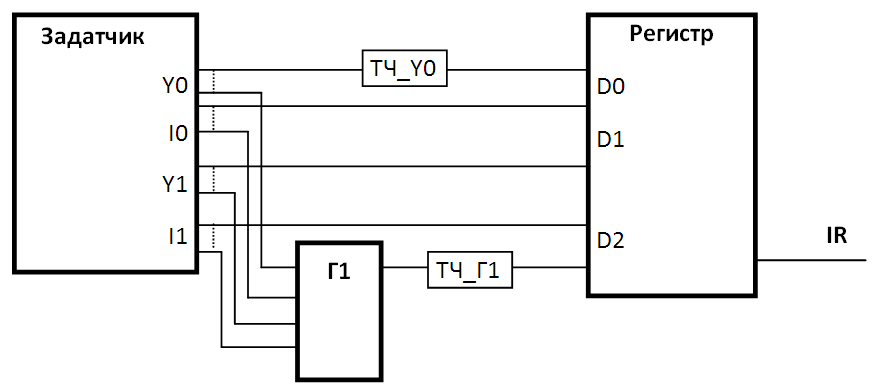

Возможности контроля параметров трасс соединений успешно реализуются на БМК. В САПР Ковчег введена также возможность фиксации подобных нарушений самосинхронности на этапе моделирования. Любая СС-функциональная ячейка, критичная к такого рода нарушениям, в таблице истинности содержит перечень запрещенных ситуаций, большая часть из которых является и/или нарушением дисциплины обмена сигналов взаимодействующих узлов СС-схемы, и/или нарушением гипотезы Маллера. Предположим, некий 4-разрядный Задатчик – элемент конвейера – является источником данных 4-разрядного Регистра на базе D-триггеров (например, D0E10) с сигналом разрешения E (см. рисунок). Взаимодействие Задатчика и Регистра предполагает, что к моменту прихода сигнала разрешения Е (сигнала записи информации в Регистр) информационные входы последнего должны иметь установившееся значение.

Иллюстрация возможного нарушения самосинхронности

На каждом выходе Yi Задатчика имеет место разветвление: внутри Задатчика каждый Yi выход заходит на вход соответствующего одноразрядного индикатора переходных процессов (отображено на рисунке штрихпунктирной линией), и они собираются на 4-входовом индикаторе переходных процессов Г1. Предположим, что транспортная задержка ТЧ_Y0 больше, чем задержка формирования сигнала E по любому из возможных путей:

ТЧ_D0 > {ТЧ_Г1 + ИЧ_Г1 +

[(ТЧ_I0*ИЧ_I0 | ТЧ_I1* ИЧ_I1 | ТЧ_I2* ИЧ_I2 | ТЧ_I3* ИЧ_I3)]}

Тогда САПР “Ковчег” зафиксирует и выдаст пользователю сообщение: “Изменения входа D запрещены до перехода входа E в спейсер”. Таким образом, САПР “Ковчег” позволит определить не только факт нарушения гипотезы Маллера (задержка проводов после разветвления не должна превосходить минимальной задержки элемента), но и нарушения дисциплины подачи информационных сигналов (Y0) и сигналов разрешения E.

Наличие программных средств анализа схем на самосинхронность на логическом уровне, базирующихся на гипотезе Маллера, и средств моделирования на физическом уровне, включающих анализ запрещенных состояний для каждого элемента схемы, позволяет проектировать два класса самосинхронных схем: не зависящих от скорости и квазинечувствительных к задержкам.

Схемы, нечувствительные к задержкам

За рубежом DI-схемы представлены Null Convention Logic (NCL) (см. Fant K.M., Brandt S.A. NULL convention logic: a complete and consistent logic for asynchronous digital circuit synthesis. «International Conference on Application Specific Systems, Architectures, and Processors» Proceedings. Chicago, 1996, pp. 261–273). Они характеризуется гораздо большей избыточностью не только в сравнении с синхронными аналогами, особенно при проектировании последовательностных схем (см. Соколов И.A., Степченков Ю.А., Бобков С.Г., Захаров В.Н., Дьяченко Ю.Г., Рождественский Ю. В., Сурков А.В. Базис реализации супер-ЭВМ эксафлопсного класса / Информатика и ее применения. М.: ТОРУС ПРЕСС, Т. 8. Вып. № 1, 2014. — С.45-70.), но и существенной избыточностью по сравнению с SI- и QDI-схемами. Причины аппаратной избыточности NCL-схем:

1) ограниченность элементного базиса (26 элементов библиотеки), использование единственного способа кодирования информационных сигналов и единственного спейсера не позволяют получать более компактные реализации последовательных схем;

2) индикация входов на выходах в каждом элементе приводит к большой избыточности аппаратных затрат;

3) вследствие аппаратурной избыточности ухудшается быстродействие и увеличивается энергопотребление.

Схемы, разрабатываемые в соответствии с методологией, продвигаемой ИПИ РАН, обладают меньшими аппаратными затратами (в 4,5 раз при реализации двоичного счетчика, в 1,13 раза при реализации умножителя 4×4, до 2 раз при реализации более простых логических схем), большей производительностью и меньшим энергопотреблением по сравнению с NCL-схемами. Поэтому именно их целесообразно использовать в качестве схемотехнического базиса для проектирования и изготовления аппаратуры с высокими надежностными показателями: они обеспечат пониженное энергопотребление и высокую надежность проектируемых цифровых устройств любой сложности.

Схемы с ограниченными задержками

Примерами этого класса схем является темпоральная (временная) логика (см. Y. Malachi and S.S. Owicki, «Temporal specification of self-timed systems,» CMU conference on VLSI Systems and Computations, 1981, pp. 203-212). Если при классическом маллеровском подходе используется гипотеза о произвольной, но конечной величине задержке элементов, то в ней используются менее жесткие гипотезы о характеристиках задержек (например, гипотеза «3/2» или «3/1»): суммарная задержка трех элементов всегда превышает задержку двух или одного элемента. Использование подобной гипотезы существенно упрощает построение общего индикатора окончания переходных процессов. При наличии в схеме n идентичных параллельных каналов (например, 64-разрядный тракт обработки информации в АЛУ) достаточно ввести в один из них один или несколько последовательно включенных повторителей (для удовлетворения требовании гипотезы). По факту окончания переходного процесса только в этом тракте делается вывод об окончании переходных процессов во всех параллельных каналах.

На этом принципе основывается так называемая спекулятивная индикация: из n-разрядного тракта обработки информации выбирается тракт с максимальной задержкой или специально добавляется задержка в один из них (см. выше), и индицируется только этот тракт. Аппаратные затраты на реализацию такого индикатора резко сокращаются, а его быстродействие увеличивается.

Следует отметить, что схемы с ограниченными задержками, в том числе и схемы, использующие спекулятивную индикацию, теряют два основных преимущества SI- и QDI-схем: они не обладают самопроверяемостью по отношению ко всем возможным константным неисправностям схемы и имеют существенно меньший диапазон работоспособности относительно внешних факторов (уровня питающего напряжения, температуры и т.д.).

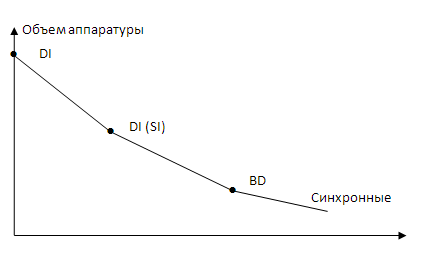

На рисунке ниже приведена зависимость аппаратных затрат на реализацию различных типов асинхронных схем в зависимости от принятой гипотезы о задержках по сравнению с синхронными схемами (рис. 1.3 из Alexander Taubin, Jordi Cortadella, Luciano Lavagno, Alex Kondratyev and Ad Peeters (2007), «Design Automation of Real-Life Asynchronous Devices and Systems», Foundations and Trends in Electronic Design Automation: Vol. 2: No. 1, pp. 1-133).

Для нас наибольший интерес представляют схемы, не зависящие от скорости, которые, в свою очередь имеют следующую классификацию:

‑ полумодулярные схемы: реализуют полумодулярную диаграмму Маллера;

‑ дистрибутивные схемы: реализуют дистрибутивные диаграммы;

‑ последовательные схемы: реализуют последовательные диаграммы.

Эти определения нужны, в основном, специалистам по разработке программных средств анализа и синтеза СС-схем, позволяющих использовать конкретные алгоритмы в зависимости от подкласса схем, не зависящих от задержки, с целью минимизации времени анализа или синтеза таких схем.

Аппаратная избыточность и степень ограничений в рамках гипотезы о задержках в асинхронных схемах

Степень ограничений в рамках гипотезы о задержках

Не претендуя на строгость, дадим пояснения приведенным терминам.

Схема является полумодулярной, если в ней каждый возбужденный элемент переходит в устойчивое состояние только путем изменения значения своего выхода. Любая полумодулярная схема не зависит от задержек. Обратное утверждение неверно. Примеры диаграмм Маллера приведен в работах Варшавского: Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под. ред. В.И. Варшавского. – М.: Наука, 1986. — 400 с. и Апериодические автоматы / Под ред. В.И. Варшавского. – М.: Наука, 1976. — 424 c.

.

Дистрибутивными являются схемы, реализованные только в базисе И-НЕ или ИЛИ-НЕ. Поэтому дистрибутивные диаграммы изменений, описывающие дистрибутивные схемы, не содержат вершин типа ИЛИ. Пример диаграммы изменений приведен при описании элемента D1CE20.

Последовательные схемы относятся к классу дистрибутивных. Каждая зона возбуждения переменных последовательной схемы состоит из единственного состояния.

Более подробно о перечисленных разновидностях схем, не зависящих от задержек, можно познакомиться в вышеупомянутых работах Мараховского и Варшавского.

Степченков Ю. А.

P.S.: Для свободного скачивания предоставляется программа анализа на цифровых схем самосинхронность САМАН, разработанная Плехановым Л. П.

Ведущий вклад в развитие самосинхронной схемотехники сделали американский профессор Дэвид Маллер и Виктор Ильич Варшавский со своими коллегами.